Development environment for RFSoC

- 720 page textbook covering DSP, SDR and ZU+ RFSoC

- Comes with 30+ open-source Jupyter Notebooks

- Right to reproduce granted for academic use

Software Defined Radio with Zynq UltraScale+ RFSoC Book

The AMD ZYNQ UltraScale+ RFSoC integrates high-speed RF signal chains, programmable logic, and multi-core ARM processors into an exceptionally powerful analog/digital system on chip. This powerful new technology is described in detail, together with a range of topics of particular interest to designers, including the RF signal chains and their high-resolution direct RF data converters, digital up- and down-converters, and quadrature mixers. Software defined radio concepts and architectures, including DSP algorithms such as multi-Nyquist zone operation, frequency planning, and multi-rate FIR filters and FFTs are also presented.

Whether you are working with software defined radios, 5G and 6G communication networks, radioastronomy systems, quantum computing or other demanding analog/digital applications, you will find a wealth of valuable information to help speed your design along.

Free .pdf at www.rfsocbook.com, or purchase from Amazon

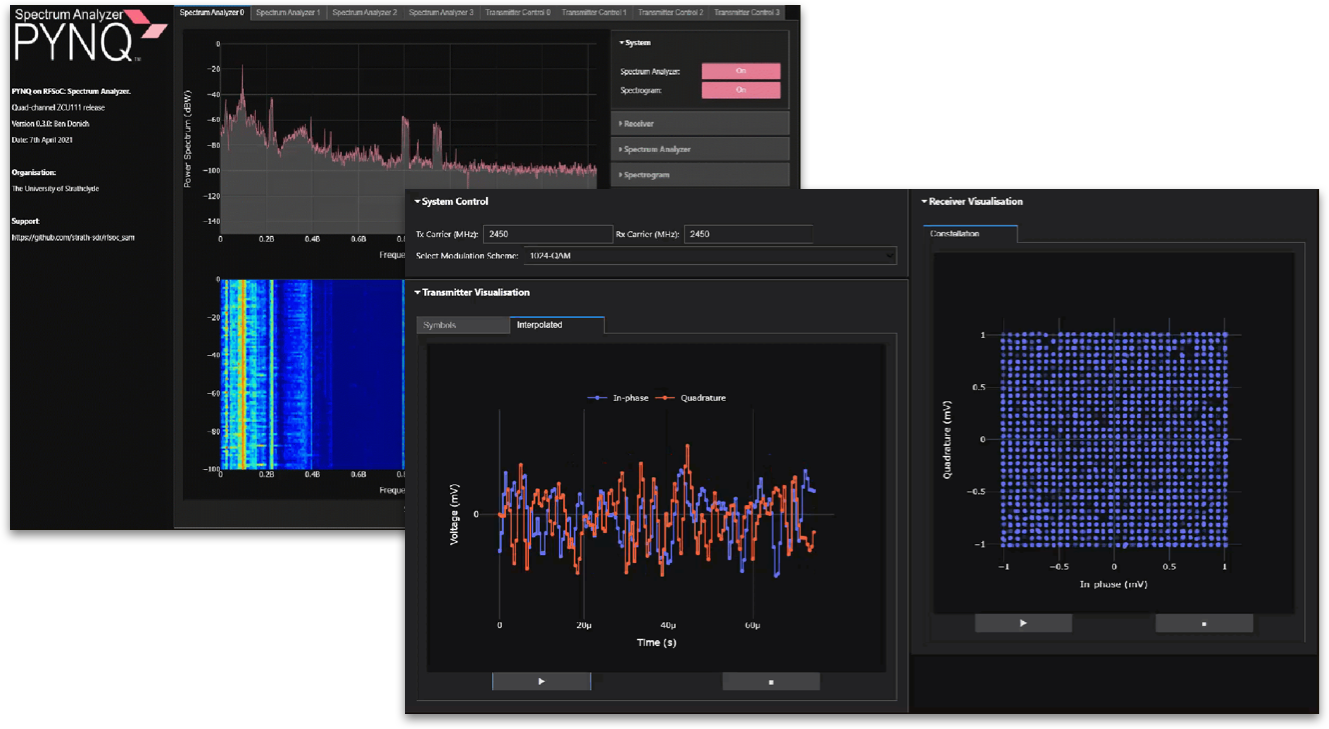

Jupyter Notebooks, Overlays, and Tutorials

The Jupyter Notebook is an open-source web application for creating and sharing documents that contain live code, equations, visualizations, and text. A notebook can run code, interact with devices, display live data, and present in-line explanations, formulas, and charts to make your work more transparent, understandable, repeatable, and shareable. RFSoC notebooks include programmable logic configurations (overlays), ARM application code, browser code to configure the board and display data – in short, everything needed to create a powerful and intuitive RF signal analysis tool.

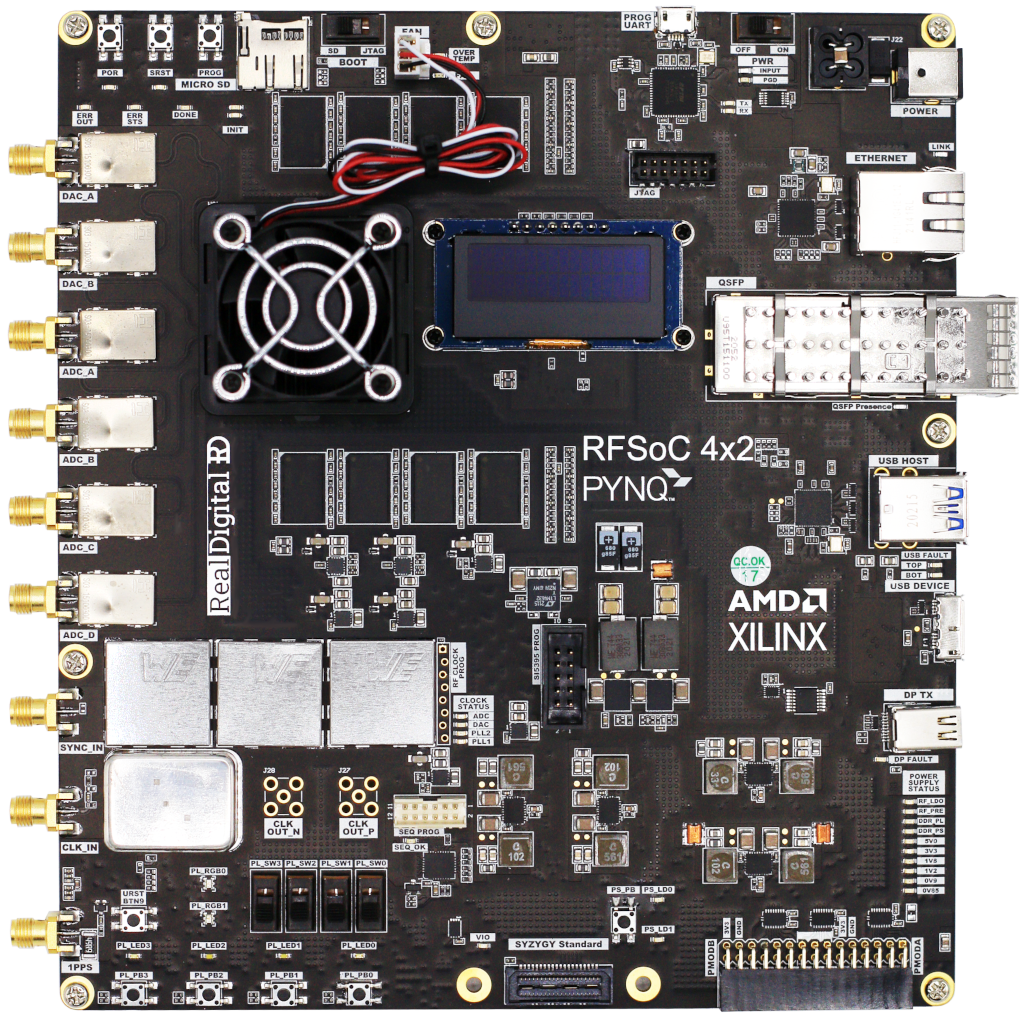

RFSoC 4x2 Board

The RFSoC 4x2 board is a complete, ready-to-use system built around the AMD Gen 3 ZYNQ Ultrascale+ RFSoC ZU48DR device. It features four 5GSPS ADC channels and two 9.85GSPS DAC channels routed to on-board SMA connectors, highly accurate clock generators, 8GBytes of 2400MHz DDR4 memory, and a 100G Ethernet QSFP28 port for high-speed data off-load.

The PYNQ Framework

The PYNQ framework greatly simplifies the process of using customized hardware in digital systems, and brings a whole new level of visualization and analysis tools to RF design environments. PYNQ uses Jupyter Notebooks, and provides a Python-based interface to configure and control programmable logic without the need for ASIC-style, hardware-centric design tools. The PYNQ framework allows the RFSoC’s resources to be accessed and controlled through prebuilt interfaces running on an attached PC, and it includes several tools for waveform visualization and analysis. PYNQ configurations are open source, and can serve as a launch point for fully custom designs.