Introduction

FIFO stands for First In First Out meaning that whatever data is written into the FIFO first will come out First when read. FIFOs are used in crossing clock domains or to create buffers in digital systems.

Setting Up FIFO in Vivado

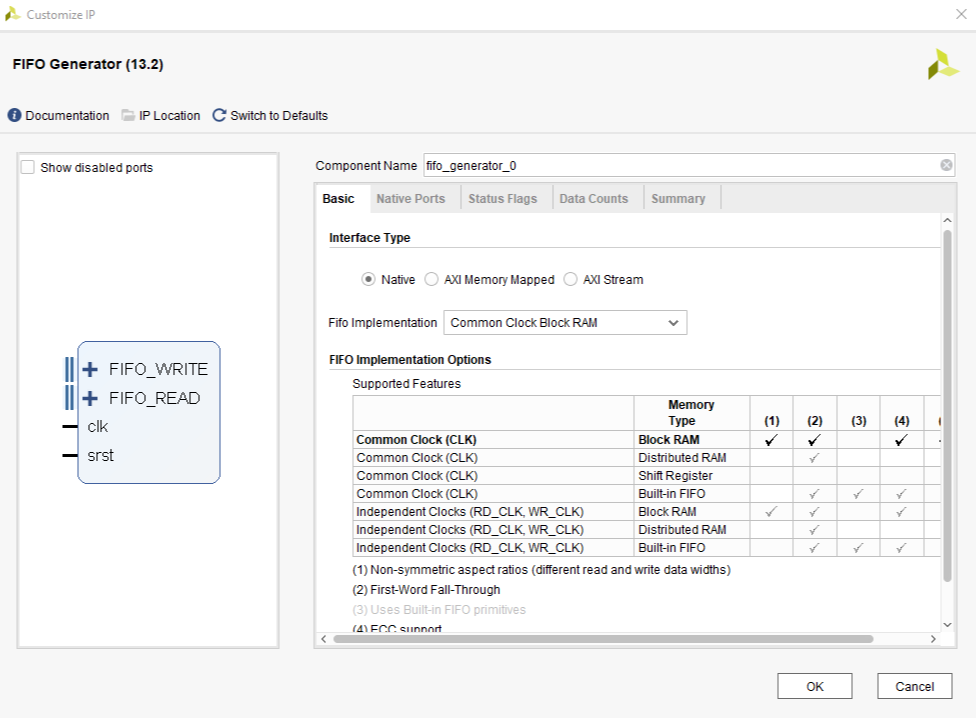

Search for FIFO Generator IP and add it to your design. Open up the IP configuration and you should be promted with the window seen in figure 1.

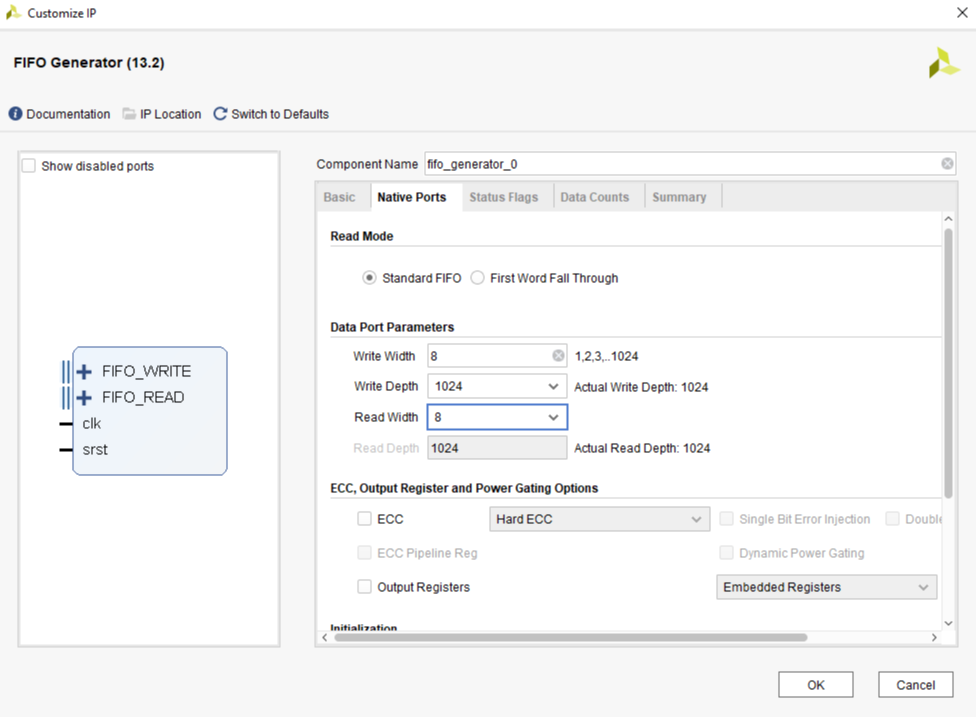

Go to native ports window and configure the write and read width based on your needs for your design.

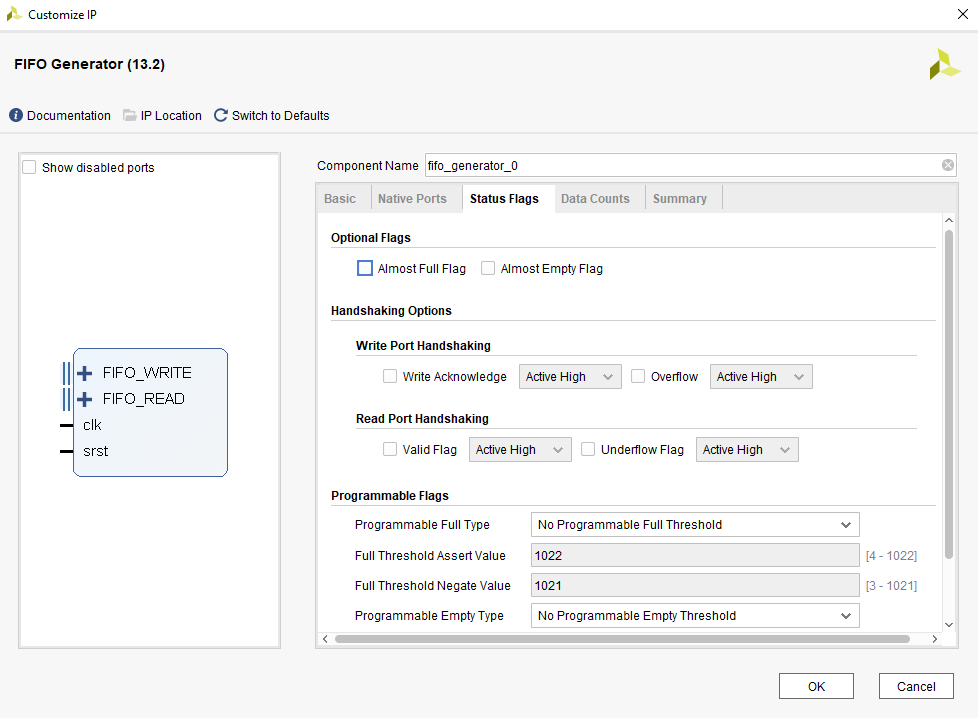

Set up almost full and almost empty status flags if needed for your design.

Interrupts for FIFO through EMIO GPIO Ports

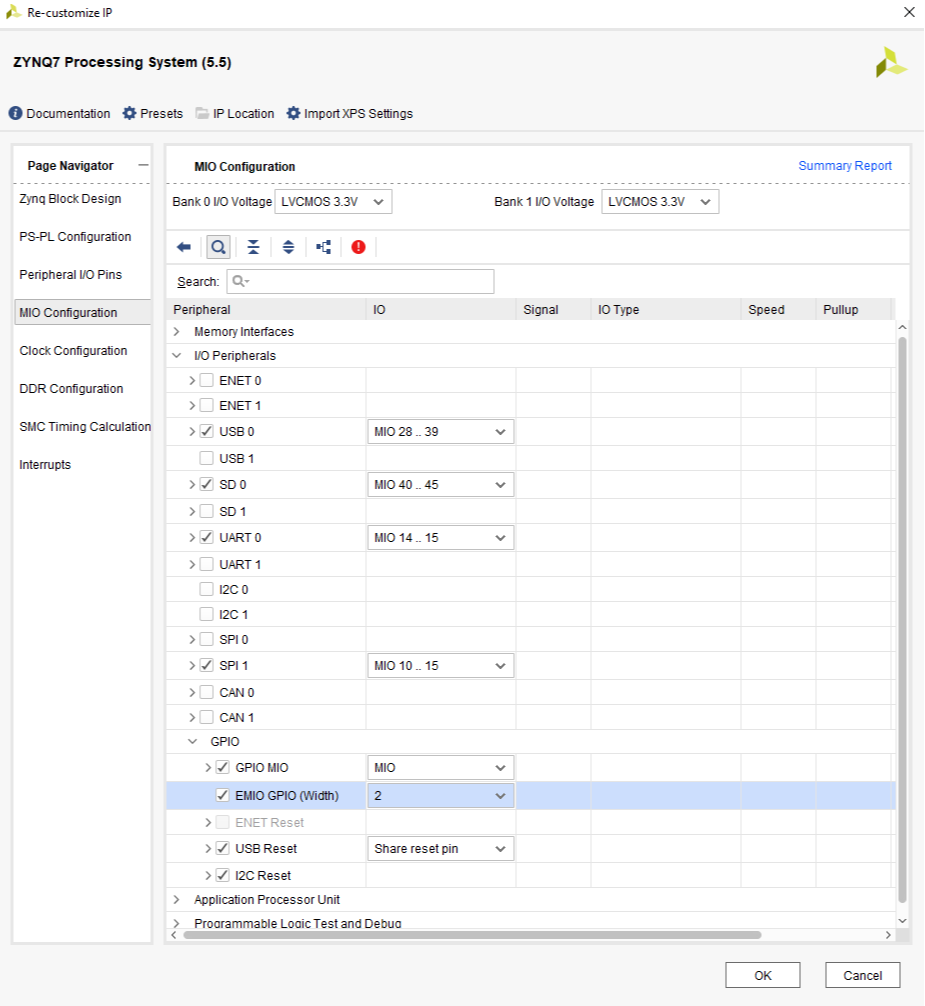

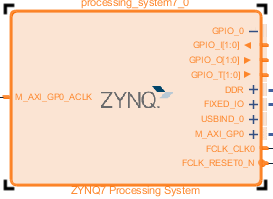

You can set up Interrupts for the FIFO through EMIO GPIO Ports. YOu can do this by opening the zynq7000 processing system.

Configure the system as shown for the EMIO GPIO as shown in figure 4.

Verify that your Zynq7 Processing system has now 2 bit wide GPIO_I bus. You can connect FIFO Full and Empty flags there.

After you’ve made the necessary connections, setup the ARM Generic Interrupt Controller interrupt #52 for GPIO Interrupt as rising edge triggered. Then configure the EMIO Pins 1:0 under the GPIO module as inputs. You can refer to the Microprocessor Systems Interrupt Controller Project for more information.