## AXI4

The AXI bus is a parallel peripheral bus that is the latest permutation of the Advanced Microcontroller Bus Architecture Standard, or AMBA.

AMBA was created by ARM in 1996 as an open-standard, on-chip interconnect specification for connecting on-chip IP blocks. It is not only used by ARM SoCs, but on a growing number of ASICs as well.

After several years of use any many interactions and improvements, the "Advanced Extensible Interface" (or AXI) protocol was added to the AMBA specification to address needs of extensible systems (easier to connect)

AMBA has become the de facto standard because it is well documented, incorporated in a wider array of exiting IP blocks, and it can be used without paying any royalties.

**AXI**, the third generation of AMBA interface defined in the AMBA 3 specification, is targeted at high performance, high clock frequency system designs and includes features that make it suitable for high speed sub-micrometer interconnect:

- separate address/control and data phases

- support for unaligned data transfers using byte strobes

- burst based transactions with only start address issued

- issuing of multiple outstanding addresses with out of order responses

- easy addition of register stages to provide timing closure.

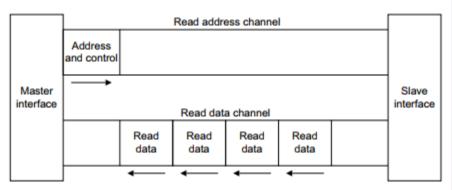

Figure A1-1 shows how a read transaction uses the read address and read data channels.

Figure A1-1 Channel architecture of reads

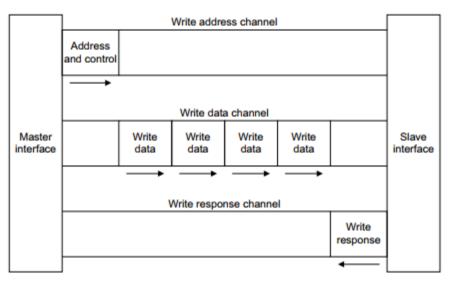

Figure A1-2 shows how a write transaction uses the write address, write data, and write response channels.

Figure A1-2 Channel architecture of writes

## Table A2-1 Global signals

| Signal  | Source       | Description                                                      |

|---------|--------------|------------------------------------------------------------------|

| ACLK    | Clock source | Global clock signal. See Clock on page A3-36.                    |

| ARESETn | Reset source | Global reset signal, active LOW. See <i>Reset</i> on page A3-36. |

All signals are sampled on the rising edge of the global clock.

## Table A2-2 Write address channel signals

| Source | Description                                                                                                                                                                                                                                     |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Master | Write address ID. This signal is the identification tag for the write address group of signals. See <i>Transaction ID</i> on page A5-77.                                                                                                        |

| Master | Write address. The write address gives the address of the first transfer in a write burst transaction. See <i>Address structure</i> on page A3-44.                                                                                              |

| Master | Burst length. The burst length gives the exact number of transfers in a burst. This information determines the number of data transfers associated with the address. This changes between AXI3 and AXI4. See <i>Burst length</i> on page A3-44. |

| Master | Burst size. This signal indicates the size of each transfer in the burst. See <i>Burst size</i> on page A3-45.                                                                                                                                  |

| Master | Burst type. The burst type and the size information, determine how the address for each transfer within the burst is calculated. See <i>Burst type</i> on page A3-45.                                                                           |

| Master | Lock type. Provides additional information about the atomic characteristics of the transfer. This changes between AXI3 and AXI4.  See <i>Locked accesses</i> on page A7-95.                                                                     |

| Master | Memory type. This signal indicates how transactions are required to progress through a system. See <i>Memory types</i> on page A4-65.                                                                                                           |

| Master | Protection type. This signal indicates the privilege and security level of the transaction, and whether the transaction is a data access or an instruction access. See <i>Access permissions</i> on page A4-71.                                 |

| Master | Quality of Service, QoS. The QoS identifier sent for each write transaction.  Implemented only in AXI4. See QoS signaling on page A8-98.                                                                                                        |

| Master | Region identifier. Permits a single physical interface on a slave to be used for multiple logical interfaces.  Implemented only in AXI4. See <i>Multiple region signaling</i> on page A8-99.                                                    |

| Master | User signal. Optional User-defined signal in the write address channel.  Supported only in AXI4. See <i>User-defined signaling</i> on page A8-100.                                                                                              |

| Master | Write address valid. This signal indicates that the channel is signaling valid write address and control information. See <i>Channel handshake signals</i> on page A3-38.                                                                       |

| Slave  | Write address ready. This signal indicates that the slave is ready to accept an address and associated control signals. See <i>Channel handshake signals</i> on page A3-38.                                                                     |

|        | Master                                                                                                                                  |

|        |        | Table A2-3 Write data channel signal                                                                                                                                                    |

|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal | Source | Description                                                                                                                                                                             |

| WID    | Master | Write ID tag. This signal is the ID tag of the write data transfer. Supported only in AXI3. See <i>Transaction ID</i> on page A5-77.                                                    |

| WDATA  | Master | Write data.                                                                                                                                                                             |

| WSTRB  | Master | Write strobes. This signal indicates which byte lanes hold valid data. There is one write strobe bit for each eight bits of the write data bus. See <i>Write strobes</i> on page A3-49. |

| WLAST  | Master | Write last. This signal indicates the last transfer in a write burst. See <i>Write data channel</i> on page A3-39.                                                                      |

| WUSER  | Master | User signal. Optional User-defined signal in the write data channel.  Supported only in AXI4. See <i>User-defined signaling</i> on page A8-100.                                         |

| WVALID | Master | Write valid. This signal indicates that valid write data and strobes are available. See <i>Channel handshake signals</i> on page A3-38.                                                 |

| WREADY | Slave  | Write ready. This signal indicates that the slave can accept the write data. See <i>Channel handshake signals</i> on page A3-38.                                                        |

|        |        | Table A2-4 Write response channel signals                                                                                                             |

|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal | Source | Description                                                                                                                                           |

| BID    | Slave  | Response ID tag. This signal is the ID tag of the write response. See <i>Transaction ID</i> on page A5-77.                                            |

| BRESP  | Slave  | Write response. This signal indicates the status of the write transaction. See <i>Read and write response structure</i> on page A3-54.                |

| BUSER  | Slave  | User signal. Optional User-defined signal in the write response channel. Supported only in AXI4. See <i>User-defined signaling</i> on page A8-100.    |

| BVALID | Slave  | Write response valid. This signal indicates that the channel is signaling a valid write response. See <i>Channel handshake signals</i> on page A3-38. |

| BREADY | Master | Response ready. This signal indicates that the master can accept a write response. See<br>Channel handshake signals on page A3-38.                    |

|          |        | Table A2-5 Read address channel signals                                                                                                                                                                         |

|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal   | Source | Description                                                                                                                                                                                                     |

| ARID     | Master | Read address ID. This signal is the identification tag for the read address group of signals. See <i>Transaction ID</i> on page A5-77.                                                                          |

| ARADDR   | Master | Read address. The read address gives the address of the first transfer in a read burst transaction. See <i>Address structure</i> on page A3-44.                                                                 |

| ARLEN    | Master | Burst length. This signal indicates the exact number of transfers in a burst. This changes between AXI3 and AXI4. See <i>Burst length</i> on page A3-44.                                                        |

| ARSIZE   | Master | Burst size. This signal indicates the size of each transfer in the burst. See <i>Burst size</i> on page A3-45.                                                                                                  |

| ARBURST  | Master | Burst type. The burst type and the size information determine how the address for each transfer within the burst is calculated. See <i>Burst type</i> on page A3-45.                                            |

| ARLOCK   | Master | Lock type. This signal provides additional information about the atomic characteristics of the transfer. This changes between AXI3 and AXI4. See <i>Locked accesses</i> on page A7-95.                          |

| ARCACHE  | Master | Memory type. This signal indicates how transactions are required to progress through a system. See <i>Memory types</i> on page A4-65.                                                                           |

| ARPROT   | Master | Protection type. This signal indicates the privilege and security level of the transaction, and whether the transaction is a data access or an instruction access. See <i>Access permissions</i> on page A4-71. |

| ARQOS    | Master | Quality of Service, QoS. QoS identifier sent for each read transaction. Implemented only in AXI4. See QoS signaling on page A8-98.                                                                              |

| ARREGION | Master | Region identifier. Permits a single physical interface on a slave to be used for multiple logical interfaces. Implemented only in AXI4. See <i>Multiple region signaling</i> on page A8-99.                     |

| ARUSER   | Master | User signal. Optional User-defined signal in the read address channel.  Supported only in AXI4. See <i>User-defined signaling</i> on page A8-100.                                                               |

| ARVALID  | Master | Read address valid. This signal indicates that the channel is signaling valid read address and control information. See <i>Channel handshake signals</i> on page A3-38.                                         |

| ARREADY  | Slave  | Read address ready. This signal indicates that the slave is ready to accept an address and associated control signals. See <i>Channel handshake signals</i> on page A3-38.                                      |

|        |        | Table A2-6 Read data channel signals                                                                                                                     |

|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal | Source | Description                                                                                                                                              |

| RID    | Slave  | Read ID tag. This signal is the identification tag for the read data group of signals generated by the slave. See <i>Transaction ID</i> on page A5-77.   |

| RDATA  | Slave  | Read data.                                                                                                                                               |

| RRESP  | Slave  | Read response. This signal indicates the status of the read transfer. See <i>Read and write</i> response structure on page A3-54.                        |

| RLAST  | Slave  | Read last. This signal indicates the last transfer in a read burst. See <i>Read data channel</i> on page A3-39.                                          |

| RUSER  | Slave  | User signal. Optional User-defined signal in the read data channel.  Supported only in AXI4. See <i>User-defined signaling</i> on page A8-100.           |

| RVALID | Slave  | Read valid. This signal indicates that the channel is signaling the required read data. See <i>Channel handshake signals</i> on page A3-38.              |

| RREADY | Master | Read ready. This signal indicates that the master can accept the read data and response information. See <i>Channel handshake signals</i> on page A3-38. |

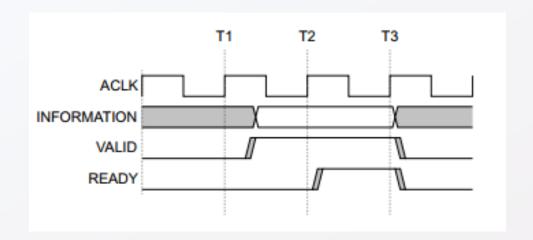

All five transaction channels use the same VALID/READY handshake process to transfer address, data, and control information. This two-way flow control mechanism means both the master and slave can control the rate at which the information moves between master and slave.

The source generates the VALID signal to indicate when the address, data or control information is available. The destination generates the READY signal to indicate that it can accept the information. Transfer occurs only when both the VALID and READY signals are HIGH.