## **Digital Logic Problem Set #1**

Revision: August 5, 2025

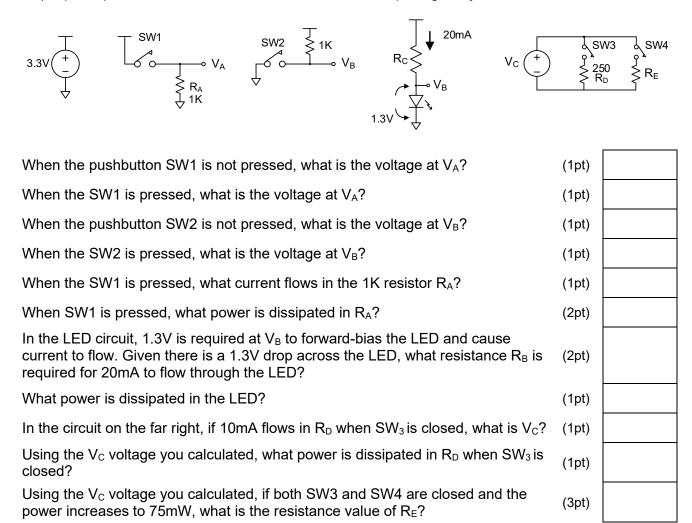

**1.** (15 points) Below are some circuit elements from a simple digital system.

Real Digital Problem Set 1

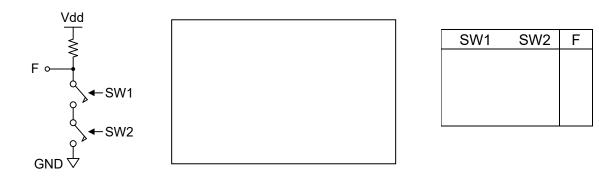

2. (20 points) The example circuit below asserts its output F as GNF (0V) when both switches are closed. Based on your reasoning for how this example circuit works, sketch a different circuit in the box below that asserts F as Vdd when both switches are closed. Label the switches 1 and 2, and complete the truth table for your circuit. Then circle the correct term (high or low, and open or closed) to complete the following sentences describing the AND and OR relationships for your new circuit.

AND Relationship: F is [Vdd / GND] when SW1 is [open / closed], and SW2 is [open / closed].

OR Relationship: F is [Vdd / GND] when SW1 is [open / closed], or SW2 is [open / closed].

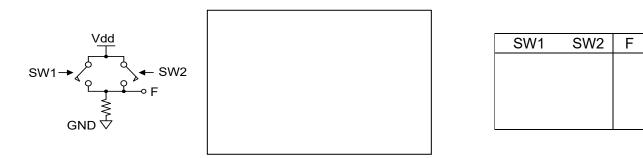

The example circuit below asserts its output as Vdd when either switch is closed. Sketch a new circuit in the box below that asserts F as GND whenever one or both switches are closed. Label the switches 1 and 2, and complete the truth table below. Circle the correct term (high or low, and open or closed) to complete the following sentences describing the AND and OR relationships for your new circuit.

AND Relationship: F is [Vdd / GND] when SW1 is [open / closed], and SW2 is [open / closed].

OR Relationship: F is [Vdd / GND] when SW1 is [open / closed], or SW2 is [open / closed].

3. (4 points) Complete the following.

A pFET turns [ ON / OFF ] with LLV and conducts [ LHV / LLV ] well (circle one in each bracket).

An nFET turns [ ON / OFF ] with LLV and conducts [ LHV / LLV ] well (circle one in each bracket).

Real Digital Problem Set 1

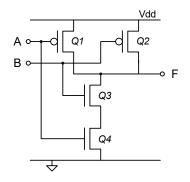

**4.** (20 points) Complete the truth tables below (enter "on" or "off" under each transistor entry, and "1" or "0" for output F), and enter the gate name and schematic shapes in the tables.

| Α | В | Q1 | Q2 | Q3 | Q4 | F |

|---|---|----|----|----|----|---|

| 0 | 0 |    |    |    |    |   |

| 0 | 1 |    |    |    |    |   |

| 1 | 0 |    |    |    |    |   |

| 1 | 1 |    |    |    |    |   |

|   |   | •  |    |    | •  |   |

| Gate<br>Name |          |

|--------------|----------|

|              |          |

| AND shape    | OR shape |

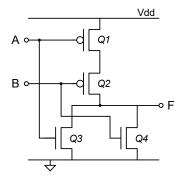

| Α | В | Q1 | Q2 | Q3 | Q4 | F |

|---|---|----|----|----|----|---|

| 0 | 0 |    |    |    |    |   |

| 0 | 1 |    |    |    |    |   |

| 1 | 0 |    |    |    |    |   |

| 1 | 1 |    |    |    |    |   |

| Gate<br>Name |          |

|--------------|----------|

|              |          |

| AND shape    | OR shape |

| _ | Α | В | Q1 | Q2 | Q3 | Q4 | F |

|---|---|---|----|----|----|----|---|

| - | 0 | 0 |    |    |    |    |   |

|   | 0 | 1 |    |    |    |    |   |

|   | 1 | 0 |    |    |    |    |   |

|   | 1 | 1 |    |    |    |    |   |

| Gate<br>Name |          |

|--------------|----------|

|              |          |

| AND shape    | OR shape |

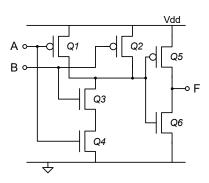

| Α | В | Q1 | Q2 | Q3 | Q4 | F |

|---|---|----|----|----|----|---|

| 0 | 0 |    |    |    |    |   |

| 0 | 1 |    |    |    |    |   |

| 1 | 0 |    |    |    |    |   |

| 1 | 1 |    |    |    |    |   |

| Gate<br>Name |          |

|--------------|----------|

|              |          |

| AND shape    | OR shape |

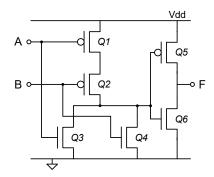

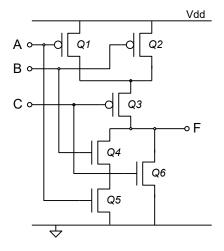

**5.** (10 points) Complete the truth table below (enter "on" or "off" under each transistor entry, and "1" or "0" for output F). Then, provide a logic equation for the circuit in the box below.

| Α | В | С | Q1 | Q2 | Q3 | Q4 | Q5 | Q6 | F |

|---|---|---|----|----|----|----|----|----|---|

| 0 | 0 | 0 |    |    |    |    |    |    |   |

| 0 | 0 | 1 |    |    |    |    |    |    |   |

| 0 | 1 | 0 |    |    |    |    |    |    |   |

| 0 | 1 | 1 |    |    |    |    |    |    |   |

| 1 | 0 | 0 |    |    |    |    |    |    |   |

| 1 | 0 | 1 |    |    |    |    |    |    |   |

| 1 | 1 | 0 |    |    |    |    |    |    |   |

| 1 | 1 | 1 |    |    |    |    |    |    |   |

F =

**6.** (12 points) Based on your knowledge of what a two-input NAND circuit and a two-input NOR circuit built from pFETs and nFETs look like, sketch a three-input NAND and four-input NOR circuit.

Real Digital Problem Set 1

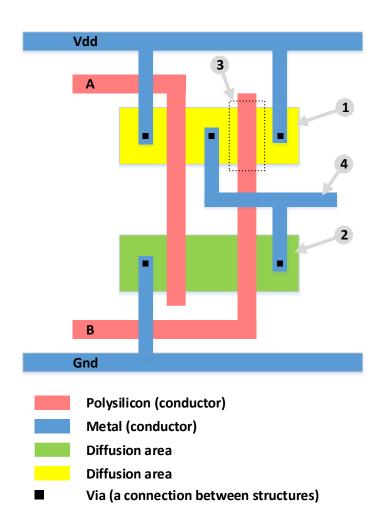

7. (8 points) The picture below shows a representation of a logic gate built from FETs as it might appear to a chip designer in a CAD/layout tool. The reddish polysilicon areas labeled A and B are conductive materials that form the circuit inputs, and the yellow and green areas are "diffusion" areas that have been implanted (or doped) with materials to make them more positive or more negative than the surrounding silicon. Based on your knowledge of CMOS gate structures, answer the following.

Which number points to the positive diffusion area?

Which number points to the negative diffusion area?

The dotted-line box pointed to by #3 represents what type of FET?

What number points to the circuit output?

What type of logic gate is this?